Statistical Variability

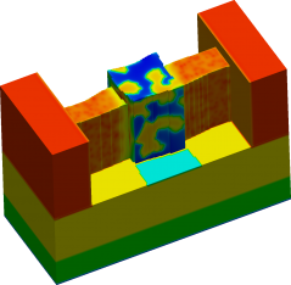

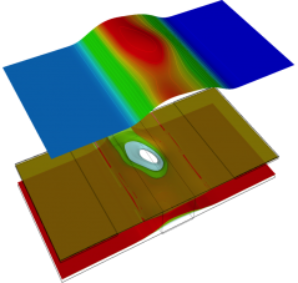

With the continuous down-scaling of semiconductor devices including MOSFETs into nanometer scale, the intrinsic parameter fluctuation introduced by discreteness of charges and granularity of matter such as random discrete dopants (RDD), line edge roughness (LER), polysilicon gate granularity (PSG) and metal gate granularity (MGG) is a significant concern in terms of device scaling and circuit yield. Those variability sources have been identified and comprehensively studied in conventional bulk transistors. In addition, the spatially random interface trapped charges (ITC) in progressive N/PBTI degradation in the background of inherent time-zero statistical variability add the statistical aspect of reliability, increasing the variability with stress time. Novel MOSFET architectures such as FD-SOI and FinFET aiming to improve short-channel effects and control statistical variability are being introduced at 22nm technology and the study of statistical variability in these architectures is critically important in evaluating further scaling and integration.

For many years members of the group have developed the world-leading statistical variability and reliability ‘atomistic’ simulator Garand. Garand has been licenced for commercial use to Gold Standard Simulations, Ltd now part of Synopsys. Now we are develeping a new in-house code called NESS that is also used to simulate statistical varibility.

Related Publications

F. Adamu-Lema, C. Monzio Compagnoni, O. Badami, V. Georgiev and A. Asenov, "RTN and its intrinsic interaction with statistical variability sources in advanced nano-scale devices: a simulation study," in Noise in Nanoscale Semiconductor Devices. Berlin: Springer, 2020, pp. 441–466.

T. Sadi, C. Medina-Ballon, M. Nedjalkov, J. Lee, O. Badami, S. Berrada, H. Carrillo-Nunez, V. P. Georgiev, S. Selberherr and A. Asenov, "Simulation of the Impact of Ionized Impurity Scattering on the Total Mobility in Si Nanowire Transistors," Materials, Vol. 12, No. 1, p. 124, 2019.

H. Carrillo-Nunez, N. Dimitrova, A. Asenov and V. Georgiev, "Machine learning approach for predicting the effect of statistical variability in Si junctionless nanowire transistors," IEEE Electron Device Letters, Vol. 40, No. 9, 2019.

X. Wang, B. Cheng, D. Reid, A. Pender, P. Asenov, C. Millar and A. Asenov, "FinFET Centric Variability-Aware Compact Model Extraction and Generation Technology Supporting DTCO," IEEE Transactions on Electron Devices, Vol. 62, No. 10, pp. 3139–3146, Oct. 2015.

A. Asenov, F. Adamu-Lema, X. Wang and S. M. Amoroso, "Problems with the continuous doping TCAD simulations of decananometer CMOS transistors," IEEE Transactions on Electron Devices, Vol. 61, No. 8, pp. 2745–2751, Aug. 2014.

X. Wang, G. Roy, O. Saxod, A. Bajolet, A. Juge, and A. Asenov, "Simulation study of dominant statistical variability sources in 32-nm high-k/metal gate CMOS," IEEE Electron Device Letters, Vol.33 no.5, pp.643-645, May 2012.

X. Wang, A.R. Brown, N. Idris, S. Markov, G. Roy and A. Asenov, "Statistical Threshold-Voltage Variability in Scaled Decananometer Bulk HKMG MOSFETs: A Full-Scale 3-D Simulation Scaling Study," IEEE Transactions on Electron Devices, Vol. 58, No. 8, pp. 2293–2301, Aug. 2011. (Cover Story)

A. Asenov, A. R. Brown, J. H. Davies, S. Kaya and G. M. Slavcheva, "Simulation of Intrinsic Parameter Fluctuations in Decananometre and Nanometre scale MOSFET's." IEEE Trans. Electron Dev. Vol. 50, pp. 1837–1852, 2003.

A. Asenov, "Random dopant induced threshold voltage lowering and fluctuations in sub-0.1 μm MOSFETs: A 3D "atomistic" simulation study," IEEE Trans. Electron Dev. Vol. 45, No. 12, pp. 2505–2513, 1998.