Compact Models

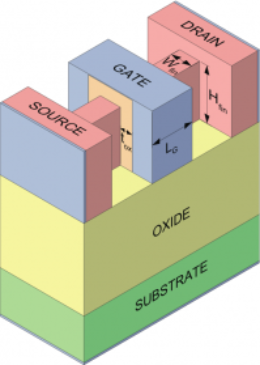

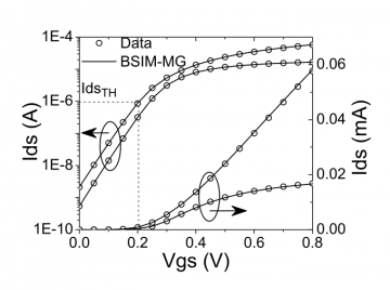

Compact Models are the bridge between technology, circuit simulations and design. Based on the compact model extraction tookit we are developing robust physics based nominal and statistical compact modelling strategies for Bulk, SOI and FinFET technologies used in our spin-off company SemiWise Ltd.

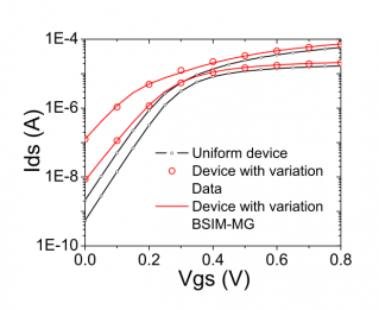

Based on the parameter sensitivity analysis, a two-stage direct statistical compact modelling extraction procedure is developed to transfer device variability information into compact models without any pre-assumption of parameter distribution and correlation. The parameter statistical distribution information obtained from direct extractioin will serve as the input for statistical parameter generation engines which have been integrated into the the Synopsys statistical circuit simulation tool RandomSpice. Our advanced parameter generation engine has the capbility to reproduce inter-parameter correlations and high moment parameter distribution information obtained from direct parameter extraction procedure.

The main advantage of our approach is the capability to accurately capture no-normality behaviour of device statistical variability, which becomes pronounced in devices at nanometer regime, with industry standard compact models. The aim of statistical compact modelling research in Glasgow is to provide a solid ground for exploration study of variability aware design of circuit and system.

Related Publications

A. Asenov, B. Cheng, X. Wang, A. R. Brown, C. Millar, C. Alexander, S. M. Amoroso, J. B. Kuang and S. Nassif, "Variability Aware Simulation Based Design-Technology Cooptimization (DTCO) Flow in 14 nm FinFET/SRAM Cooptimization," IEEE Transactions on Electron Devices, Vol. 62, No. 6, pp. 1682–1690, June 2015.

X. Wang, B. Cheng, D. Reid, A. Pender, P. Asenov, C. Millar and A. Asenov, "FinFET Centric Variability-Aware Compact Model Extraction and Generation Technology Supporting DTCO," IEEE Transactions on Electron Devices, Vol. 62, No. 10, pp. 3139–3146, Oct. 2015.

X. Wang, D. Reid, L. Wang, A. Burenkov, C. Millar, J. Lorenz and A. Asenov, "Hierarchical Variability-Aware Compact Models of 20nm Bulk CMOS," in Proc. 20th International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Washington DC, Sept. 9-11, 2015, pp. 325–328.

B. Cheng, D. Dideban, N. Moezi, C. Millar, G. Roy, X. Wang, S. Roy, A. Asenov, “Statistical-Variability Compact-Modeling Strategies for BSIM4 and PSP”, IEEE Design & Test of Computers, Vol. 27, issue 2, pp.26-35, 2010, Invited.

A. Asenov, B. Cheng, D. Dideban, U. Kovac, N. Moezi, C. Millar, G. Roy, A. Brown, S.Roy, “Modelling and Simulation of Transistor and Circuit Variability and Reliability”, Proceedings of IEEE Custom integrated Circuits Conference, 2010, invited.

U. Kovac, D. Dideban, B. Cheng, N. Moezi, G. Roy, A. Asenov, “A novel approach to the statistical generation of non-normal distributed PSP compact model parameters using a nonlinear power method ”, Proceedings of Simulation of Semiconductor Process and Devices, 2010.