Circuit Simulation

Circuit simulation is essential for functional logic verification, timing closure and power analysis – a combination of which can allow circuit yield estimation, an important metric in determining the success of a design and the profitability of a product. Timing closure, states that if maximum latch-to-latch delay in a system is D, with clock period T and latch setup time L, in order for a system to fulfill timing requirements, the maximum delay (often extracted by predictive simulation) is: D=T-L.

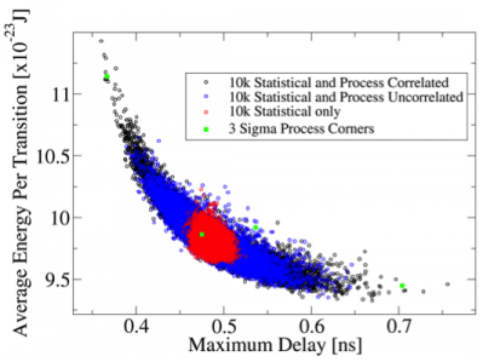

The aim of our work is to investigate ways to propagate device level variability information to designers in such as way as to provide power/performance and yield predictions which can inform and aid the design and design evaluation process.

Related Publications

P. Asenov, N. A. Kamsani, D. Reid, C. Millar, S. Roy and A. Asenov, "Combining Process and Statistical Variability in the Evaluation of the Effectiveness of Corners in Digital Circuit Parametric Yield Analysis," European Solid-State Circuits Conference: Sept. 13-17, 2010.

D. Dideban, B. Cheng, N. Moezi, N. A. Kamsani, C. Millar, S. Roy and A. Asenov, "Impact of Input Slew Rate on Statistical Timing and Power Dissipation Variability in nano CMOS," in Proc. Ultimate Integration on Silicon, Glasgow, Scotland, UK, Mar. 17-19, 2010, pp. 45–48.

N. A. Kamsani, B. Cheng, S. Roy and A. Asenov, "Impact of Random Dopant Induced Statistical Variability on Inverter Switching Trajectories and Timing Variability," in Proc. IEEE International Symposium on Circuits and Systems, Taipei, Taiwan, May 24-27, 2009